Hej,

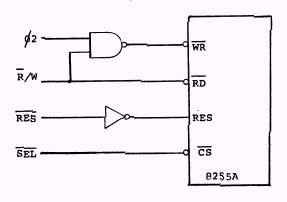

Znalazlem w starych 'scalakach' calkiem zwawego 8255. Moze mi ktos nakreslic prosty schemat jak to podpiac do atari zeby uzyskac dostep do niego?

Adresy/Dane wiem jak podlaczyc, gorzej ze zdekodowaniem tego na jakims $Dxxx. Wiem ze podlaczano swego czasu drugie PIA w atari, a 8255 sie wiele nie rozni, wiec chyba to bedzie dosc trywialne. Jesli by mi sie to udalo to bym mial pomysl na nowe rozszerzenie do atari :)

EDIT:

74138 da rade chyba, tylko jak to podpiac :)