Witajcie!

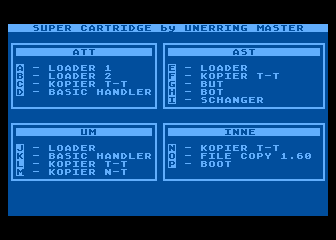

Dzięki uprzejmości Nosty-ego możecie mieć do dyspozycji zrekonstruowany "Unerring Master Super Cartridge". Jest to cartridge zawierający loadery i kopiery dla systemów turbo zgodnych z AST, ATT, UM. Z dyskusji wcześniej prowadzonych na tym forum wynika iż magnetofony wyposażone w turbo Blizzard również powinny działać z oprogramowaniem zawartym na tym cartridge. Dla przypomnienia, cartridge po uruchomieniu wygląda tak:

Jest to typowy 16KB cartridge, z możliwością odłączenia go poprzez dowolny zapis pod dowolną lokację z zakresu $D500-$D5FF. Zawartość pamięci EPROM tego cartridge możecie pobrać tutaj: UM Super Cartrige EPROM. Plik ten można również uruchomić pod emulatorem Atari800 czy Aatari800Win wybierając jako typ cartridge "Blizzard 16KB cartridge".

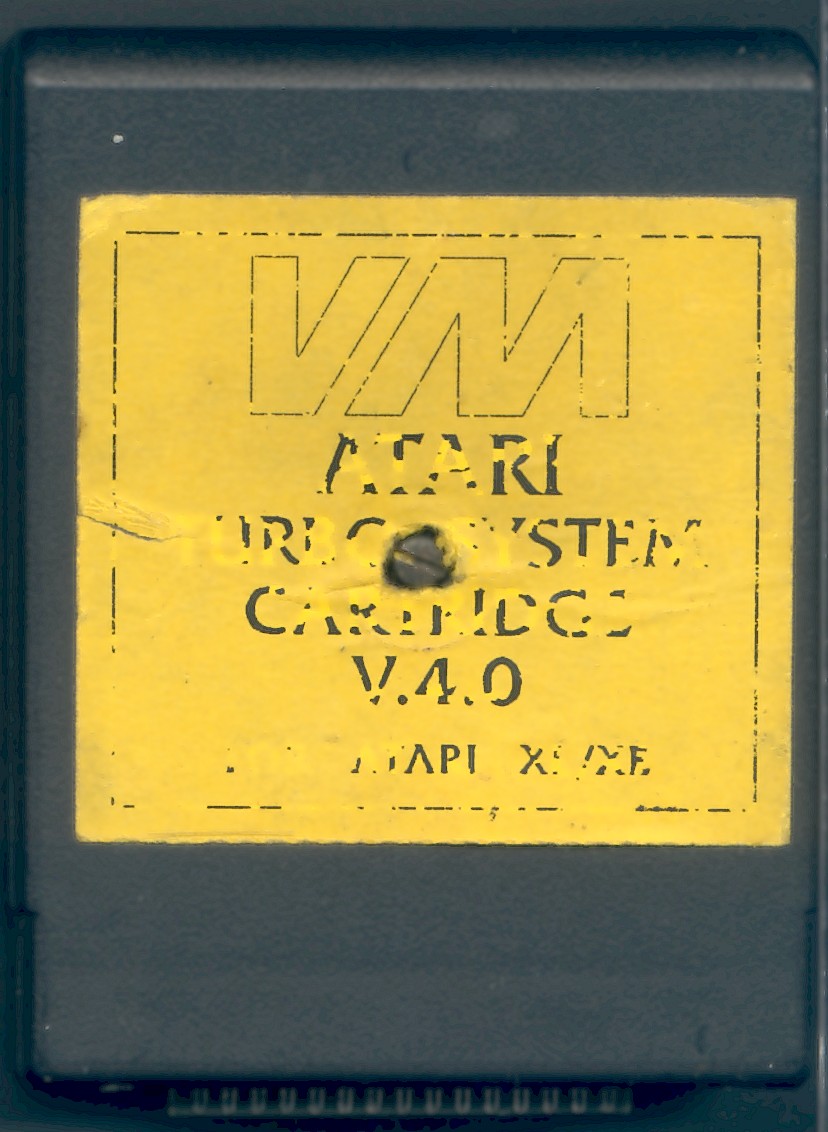

Cartridge wyglądał w ten sposób:

Może nasz naklejkowy renowator szanowny "kierownik zamieszania" ;) zechce zrekonstruować również tą naklejkę? :) Jeżeli tak to w razie potrzeby skan karta w 300dpi TIFF jest tutaj.

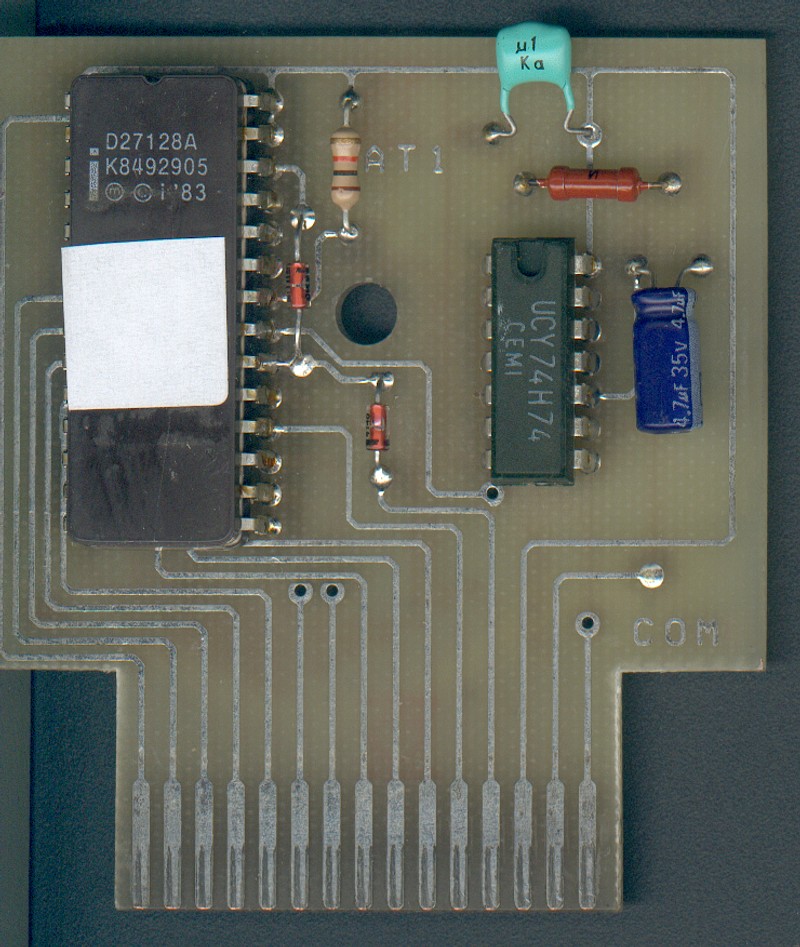

Dół płytki drukowanej (tzw. PCB) zawierającej komponenty wygląda tak:

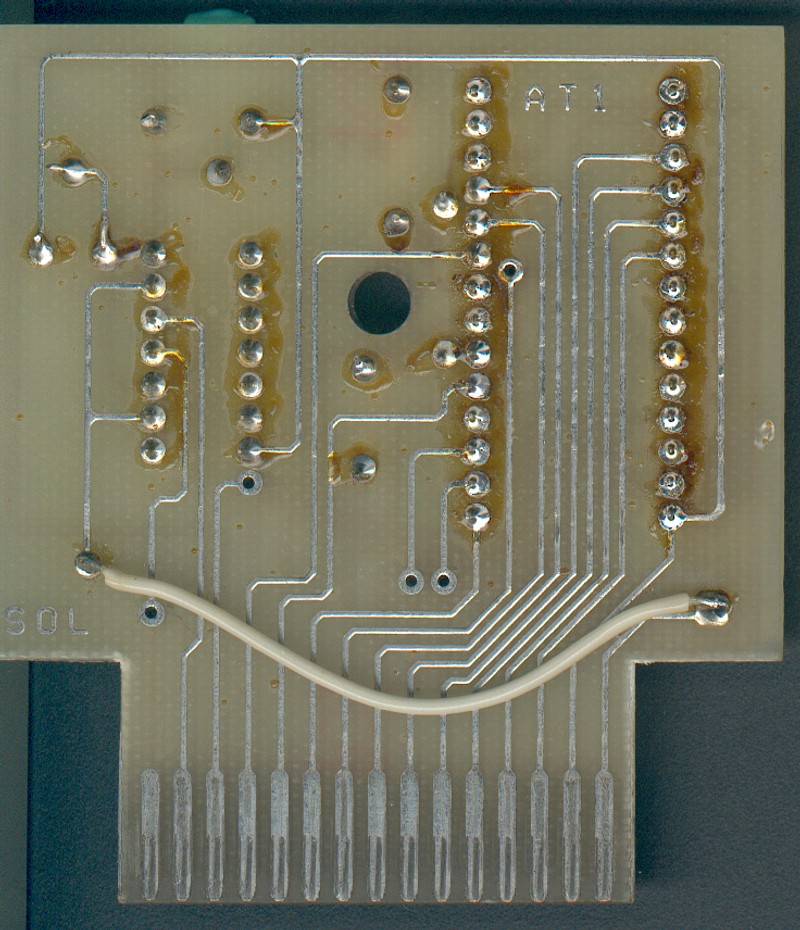

Góra PCB wygląda tak:

Dla zainteresowanych rozrysowany schemat cartridge:

wersja PDF: schemat w formacie wektorowym PDF

wersja PNG: schemat w formacie rastrowym PNG

Patrząc na schemat możemy wydzielić dwa funkcjonalne bloki:

1) 16KB pamięć EPROM 27128 podpiętą do magistrali ATARI poprzez sygnały A0-A12, oraz D0-D7. Diody D1, D2 oraz rezystor R2 tworzą prosty układ zastępujący bramkę OR. Pojawienie się zera logicznego na którejkolwiek z linii (~S4 lub ~S5) powoduje wymuszenie zera logicznego na liniach ~OE i ~CE pamięci EPROM, co spowoduje podpięcie jej pod magistralę w momencie kiedy na magistrali adresowej wystąpi adres z zakresu $8000-$8FFF (pojawia się wtedy zero logiczne na linii ~S4) lub $A000-$BFFF (pojawia się wtedy zero logiczne na linii ~S5). Ponieważ w złączu cartridge ATARI mamy tylko linie A0-A12 co umożliwia zaadresowania 8KB, a EPROM mamy 16K... sygnał ~S4 jest również wykorzystany do sterowania linią A13 pamięci EPROM, a co za tym idzie do wyboru odpowiednich 8K z pamięci EPROM.

2) Drugi blok to układ zapewniający możliwość całkowitego odłączenia cartridge poprzez zapis dowolnej wartości pod adres z zakresu $D500-$D5FF. Do tego celu został wykorzystany przerzutnik typu D (dwa takie znajdują się w układzie scalonym 74H74). Po włączeniu zasilania przerzutnik jest ustawiany tak aby na jego wyjściu Q pojawiła się logiczna 1. Jest to realizowane poprzez układ RC, składający się z rezystora R1 oraz kondensatora C1. W chwili włączenia zasilania napięcie na kondensatorze jest bliskie zera, co powoduje iż wejście asynchroniczne wejście SET przerzutnika zostaje wyzwolone i na wyjściu Q pojawia się stan 1. Kondensator zostaje naładowany przez rezystor R1 i przerzutnik pozostaje w takim stanie do czasu gdy nastąpi dowolny zapis pod adres $D500-$D5FF. Gdy dojdzie to takiej sytuacji na wyjściu Q przerzutnika pojawia się zero logiczne co powoduje odłączenie cartridge poprzez podanie tego zera na wejścia RD4 oraz RD5. Dodatkowo wyjście Q jest połączone z asynchronicznym wejściem zerującym przerzutnik RESET (aktywne w stanie zero). Następuje swego rodzaju dodatnie sprzężenie zwrotne i przerzutnik pozostaje w tym stanie (Q=0) do momentu wyłączenia zasilania.

Układ odłączania karta zawiera moim zdaniem drobny błąd konstrukcyjny i działa on zapewne przez przypadek :) Mianowicie... do wykrycia zapisu pod adres $D500-$D5FF potrzeba dwóch sygnałów... właśnie ~CCTL, który informuje o pojawieniu się na magistrali adresowej adresu z przedziału $D500-$D5FF, ale do tego trzeba jeszcze określić czy chodzi o odczyt czy o zapis danych. Do tego celu należy wykorzystać sygnał R/~W. Gdy jest on w stanie 1 informuje on nas iż mamy do czynienia z odczytem danych gdy jest on w stanie 0 wiemy iż chodzi o zapis danych. Ten fakt chciał wykorzystać twórca tego cartridge jednak popełnił on błąd. Przerzutnik typu D (taki jak 7474) przepisuje dane z wejścia D na wyjście Q w momencie gdy pojawi się narastające zbocze zegarowe na wejściu CLK. Jednak w tym wypadku sygnał ~CCTL cały czas utrzymuje się w stanie wysokim a jedynie podczas pojawiania się adresów $d5xx przechodzi do stanu niskiego aby zasygnalizować tan fakt. Również w tym momencie sygnał R/~W ma już ustaloną wartość. Nasz przerzutnik nie zapamiętał jeszcze stanu sygnału R/~W bo nie wystąpiło jeszcze żadne narastające zbocze na wejściu CLK (~CCTL jest w stanie niskim). W następnym cyklu na magistrali (gdy już nie ma dostępu do $D5xx) sygnał ~CCTL zmienia wartość z 0 na 1 w właśnie w tym momencie jest zapamiętywana wartość sygnału R/~W... jednak może być ona już nie aktualna... bo powinna ona być zapamiętana przy opadającym zboczu ~CCTL. Więc dlaczego to działa poprawnie? Sądzę iż dzięki opóźnieniom sygnału R/~W, być może jeszcze przez chwilę zachowuje on poprawną wartość którą udaje się zatrzasnąć w przerzutniku :)

*) symbol "~" którego używałem oznacza negację, czyli opis ~CCTL oznacza iż stanem aktywnym tego sygnału jest stan niski (zero logiczne)

Ufff... ale po co ja wam to wszystko opowiadam :) Pewnie i tak nikogo to nie interesuje :) Tak czy inaczej kolejny relikt z naszej przeszłości mógł zostać uratowany z czeluści zapomnienia :)

Wielkie podziękowania należą się dla kolegi Nosty-ego za chęć wypożyczenia tego cartridge do analizy i dokonania dump-a oraz reverse engineering-u :) DZIĘKI WIELKIE NOSTY! :D

pozdrawiam

Seban