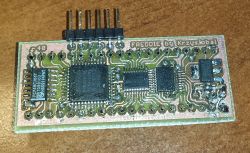

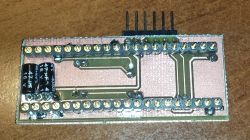

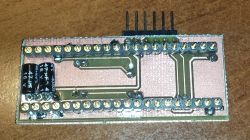

Znalazłem chwilę, wytrawiłem płytki i wszystko działa bez zarzutu.

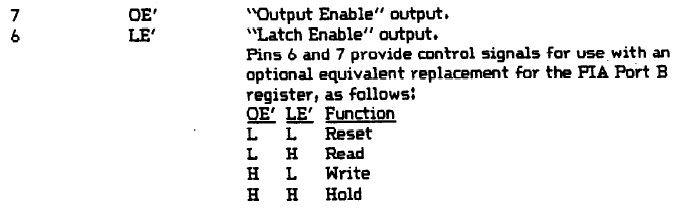

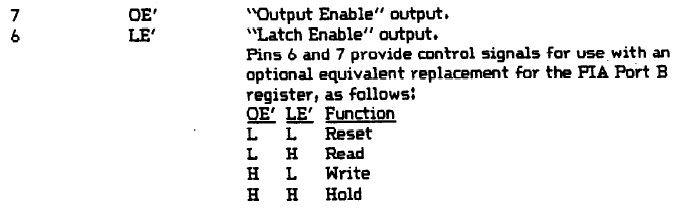

Ciągle jeszcze nie dawały mi spokoju piny 6 i 7 (/LE i /OE).

W oficjalnej dokumentacji Freddyego:

Miałem pewne przeczucie, że te piny w jakiś sposób zależą od linii adresowych, więc musiałem stworzyć ulepszoną wersje testera, która będzie w stanie wysterować i spróbkować wszystkimi 38 pinami tego scalaka (40 - vcc - gnd)

/OE:

Jeśli na linii adresowej jest $D301 oraz RW=1, /OE idzie w górę po pierwszym zboczu narastającym CKIN

Jeśli na linii adresowej jest inny adres lub RW=0, /OE idzie w dól po pierwszym zboczu narastająym CKIN

Gdy O2=0, /OE idzie w dół po 8, a potem w górę po 18 zboczu (narastajacym lub opadajacym)

/LE:

Jeśli na linii adresowej jest $D301 oraz RW=0, /LE idzie w górę po pierwszym zboczu narastającym CKIN

Jeśli na linii adresowej jest inny adres lub RW=1, /LE idzie w dól po pierwszym zboczu narastająym CKIN

Gdy O2=0, /LE idzie w dół po 8, a potem w górę po 14 zboczu (narastajacym lub opadajacym)

CK_IN _.-._.-._.-._.-._.-._.-._.-._.-._.-._.-._.-._.-._

2 4 6 8 10 12 14 16 18

1 3 5 7 9 11 13 15 17 |19

| | | | | | | | |

PHI2 -----------.______________________________________

nOE ______________.-----------.___________________.--

RW ______--------------------------------------------

nLE ______________.-----------.___________.----------

RW -------___________________________________________

To wszystko niestety sprawia, że układ CPLD potrzebuje wszystkich 16 linii adresowych do pełnego dekodowania adresu.

fedcba9876543210

0b1101001100000001 = $D301

W powyższej wersji płytki, CPLD w ogóle nie brał pod uwagę tych linii, bo ich multipleksowaniem zajmowały się bufory.

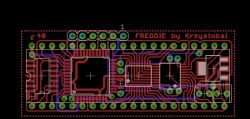

Postanowiłem wiec zaprojektowac kolejną wersje płytki, któa doprowadzałaby wszystkie linie do CPLD, wtedy bufory już w ogóle nie będą potrzebne, bo multipleksacją zajmie się też CPLD.

Niestety jak wspominałem wcześniej, CPLD nie ma wystarczająco dużo pinów, aby temu sprostać.

Można wykorzystać cztery piny JTAGa jako piny IO (wtedy do zaprogramowania układu potrzeba napięci +12V), ale nadal zabraknie nam trzech pinów:

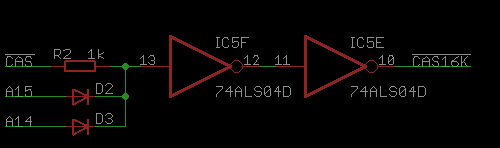

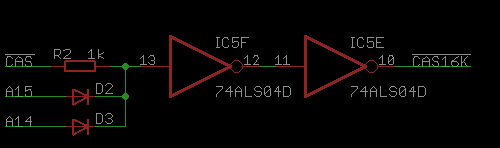

- linię nCAS16k (=nCAS or A14 or A15) można zamiast w CPLD, generować na diodzie i rezystorze, a nieużywana bramka 74HCU04 będzie pełnić rolę bufora i regeneracji napęcia, zyskujemy więc jeden pin:

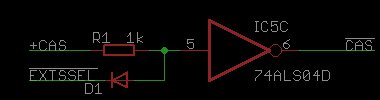

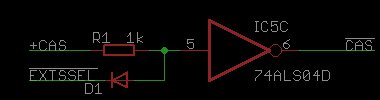

- linia /EXTSEL także może być dekodowana zamiast przez CPLD, to za pomocą iody i rezysora - zyskujemy kolejny pin (wtedy ukłąd CPLD musi generować odwrócony sygnał CAS, oznaczony na schemacie jako +CAS):

Długo zastanawiałem się, skąd wytrzasnąć ostatni pin, aż w końcu wpadłem na genialny pomysł:

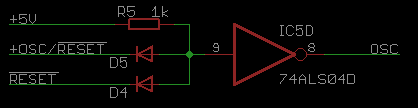

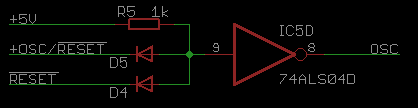

Wykorzystałem fakt, że CPLD może jeden pin traktować jako `in`, `out` lub `inout` i linię OSC i /RESET połączyłem w jedną:

- układ CPLD gdy wcześniej wystawiał na lini OSC sygnał 0/1, teraz wystawia sygnał 0/H, a zewnętrzny pull-up 1k podciąga tą linię w górę (bramka 7404 regeneruje sygnał, zwiększająć jego wydajność prądową)

- w sytuacji gdy nRESET ma stan wysoki, nie wplywa on na funkcję tej linii; gdy nRESET ma stan niski, za pomocą D4 ściąga on tą linię w dół

- układ CPLD próbkuje tą linię w sytuacji, gdy wystawia na niej H (wysoka impedancja). Jeśli na linii odczytał 1 to znaczy, że nRESET jest 1, a jeśli odczytał 0 to znaczy, że nRESET jest 0.

W ten sposób układ może odzyskać z tej linii sygnał RESEET.

Jedyna niedogodność (i niezgodność) z oryginalnym Freddym jest więc taka, że w sytuacji gdy nRESET=0, linia OSC nie będzie generować sygnału zegarowego, ale to chyba nie bedzie mieć znaczenia (w Atari 65XE linia nRESET ma stan niski jedynie w chwili gdy komputer włącza się po podaniu zasilania; wciskanie klawisza RESET na klawiaturze nie powoduje aktywacji tej linii)

Jak zamówię płytki w fabryce, będę mógl wam podesłać układy do testów. Czy cena w okolicach 60zł jest akceptowalna?

Czy znacie jakiś komputer który wykorzystuje linie /LE i /OE z Freddyego, aby dało się przetestować poprawność tej realizacji?