Czy ktoś pomógłby mi przeanalizować przebieg sygnału zegarowego w Atari 800XLF?

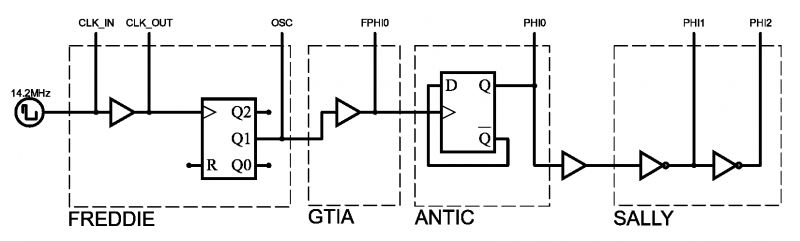

Zaczynamy od generatora kwarcowego 14,1875 MHz, sygnał CLK wchodzi na FREDDIEgo na pin 2, gdzie jego częstotliwość jest dzielone przez 4 i wychodzi z niego jako sygnał OSC (3,55 MHz) z pinu 37. OSC idzie dalej do GTIA do pinu 28 i wychodzi jako FPHI0 z pinu 29. Dalej trafia do ANTICa na pin 35, gdzie jest dzielony przez 2 i wychodzi jako PHI0 (1,77 MHz) z pinu 34, aby ostatecznie, przez bufor, trafić do SALLY na pin 37. SALLY generuje z niego 2 pomocnicze sygnały zegarowe: PHI1 (pin 3) i PHI2 (pin 39). Sygnał PHI2 wraca (?!?) do FREDDIEgo (pin 5), ANTICa (przez bufor, na pin 29), oraz GTIA (pin 30). PHI1 jest używany w układzie korekty (fazy) koloru "przy" GTIA. PHI2 jest prawie "w fazie" z PHI0 (opóźniony o kilkadziesiąt ns), a PHI1 jest odwrócony w fazie o 180° względem PHI2.

Czy coś pominąłem albo przekręciłem? Nie mogę pojąc dlaczego ten sygnał dociera do SALLY tak pokrętną drogą i po co tym wszystkim układom dodatkowo sygnał PHI2 z SALLY? Bez PHI0 nie ma przecież ani PHI1 ani PHI2.